射频变压器能够实现阻抗、电压、电流的变换,且具有隔直(流)、共模抑制及单端转差分(或称为非平衡转平衡)功能,所以被广泛应用于射频电路诸如推挽放大器、双平衡混频器及A/D ICs中。对于这类阻抗变换器件,其单端阻抗往往不是50 Ohm,给性能测试制造了重重困难。

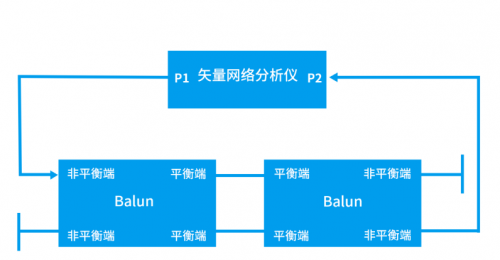

相对于传统back-to-back这种背靠背测试方法的局限性,下面将为大家展示一种基于矢量网络分析仪的测试方法。

使用这两项功能可以很有效地测试射频变压器的性能指标。

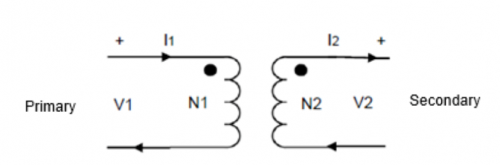

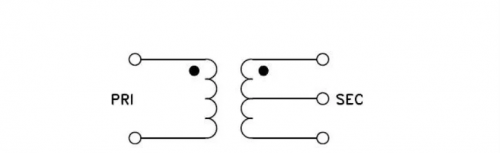

射频变压器一般由两个或多个彼此绝缘的铜导线绕至在磁芯上而成,通过电磁耦合实现功率由初级(Primary)到次级(Secondary)的传输。图1给出了射频变压器的等效电路,假设初级线圈绕线匝数为N1,次级线圈绕线匝数为N2,则满足如下关系:

N2 / N1 = n, V2 = n × V1, I1 = n × I2 (式1)

输入、输出阻抗变换比为:Zout / Zin = (N2 / N1)2 (式2)

图1. 射频变压器等效电路

如何测试射频变压器的性能呢?

大多数射频变压器可以实现不平衡到平衡的转换,对于这样的变压器,可以将其当作一个Balun,测试参数包括:插损、回损、CMMR、幅度和相位不平衡特性等。

对于单端阻抗为50 Ohm、差分阻抗为100 Ohm的变压器,可以直接在矢网的虚拟差分测试模式下测试,因为默认情况下,失网在虚拟差分模式下的单端阻抗和差分阻抗是与待测射频变压器匹配的。但是对于单端阻抗不是50 Ohm的变压器,如何有效测试其性能呢?

如果射频变压器的单端阻抗不是50 Ohm,需要考虑待测件与矢网之间的端口匹配。传统的测试方法是,直接使用两个相同的射频变压器back-to-back布置,从而实现阻抗的匹配,如下图所示测得的插损取一半即为单个变压器的插损。该方法能够测试变压器的插损和回损,但是无法有效测试CMMR和幅度、相位不平衡特性。

(传统back-to-back法射频变压器测试)

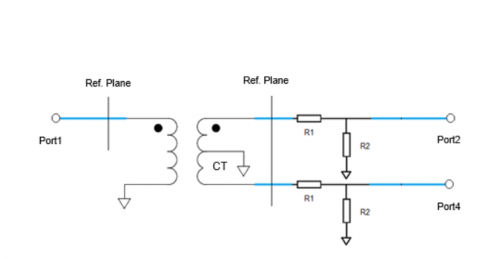

或者使用如图2所示的阻抗变换器,使用两个电阻搭建Mini-Loss Matching PAD。如果平衡端差分阻抗为200 Ohm,则对应的单端阻抗为100 Ohm。R1和R2的取值要同时保证,从DUT输出向矢网看去的输入阻抗为100 Ohm,及从矢网向DUT看去的输入阻抗为50 Ohm。图3给出了相应的测试装置示意图,采用UOSM校准方式。Port1与Port2、Port4之间的直通校准,也需要连接一个阻抗变换网络,以实现端口之间的匹配。

图2. Mini-Loss Matching PAD

图3. 采用阻抗变换器的测试装置示意图

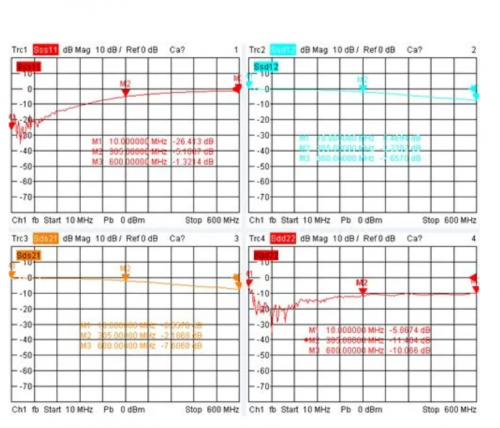

校准完成后,测试了某一款射频变压器的插损、回损等参数,如图4所示。低频时,测试结果与规格指标比较一致,但是随着频率的提高,偏离规格指标越来越大。经实验发现,阻抗变换器所使用的电阻的频率特性较差,电阻值随频率的增加变化较大,这限制了该方法在高频时的应用。

图4. 使用阻抗变换器时的测试结果

目前大部分矢网都支持更改端口参考阻抗,在一定条件下,这允许测试非50 Ohm系统阻抗下的S参数。其大致原理:首先测试50 Ohm系统阻抗下的S参数,然后根据所设置的端口参考阻抗,对测试数据作相应的数学变换,从而得到其它系统阻抗对应的S参数。如此,就不需要外部的阻抗变换器,使得测试更加灵活。

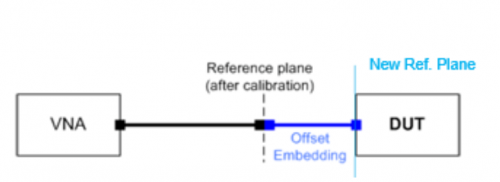

对于射频变压器,输出为差分形式,设计测试评估板时,PCB走线的阻抗及线间距均应按照一定的规则布置,以减少对测试结果的影响。但实际中,这一点往往很难满足。为此,校准完成后,需要执行Offset功能,将校准参考面延伸至待测件pin处。这一点很重要,尤其对于差分端,因为评估板走线一般是按照50 Ohm进行阻抗控制的,而射频变压器差分输出端的单端阻抗往往不是50 Ohm,如果不作Offset,则测试结果将偏差很大。

图5. Offset示意图

1射频变压器参数如下:

输入单端阻抗:50 Ohm

阻抗变换比:1:4

频率范围:0.5MHz~600MHz

带内插损 (Spec.):≤ 3dB

测试步骤:

① 首先设定频率范围,并执行系统误差校准,此时按照默认的50 Ohm端口参考阻抗即可;

② 然后执行端口延伸功能,尤其是对差分端口;如果待测件输入侧单端阻抗不是50 Ohm,建议对单端端口也作端口延伸;

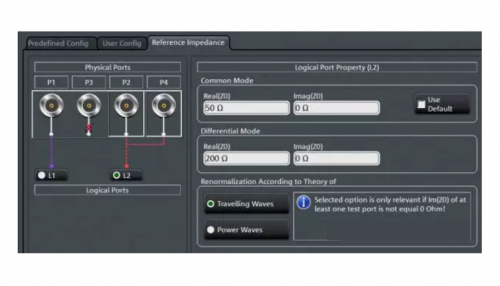

③ 最后进入虚拟差分测试模式,并将差模、共模阻抗按照变压器的实际阻抗值输入。

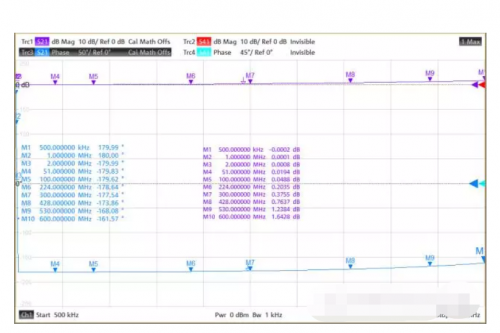

图6和图7分别给出了待测射频变压器的插入损耗、回波损耗及幅度和相位不平衡特性测试结果,其中插入损耗在全频段满足规格指标,但是在高频处,幅度和相位不平衡特性较差,这会影响对共模干扰信号的抑制能力。对于图1所示的这种次级含有中心抽头的射频变压器,一般建议将中心抽头接地,可以改善幅度和相位不平衡特性。

图6#变压器插入损耗和回波损耗测试结果

图7#变压器幅度和相位不平衡特性测试结果

图8#变压器插入损耗和回波损耗测试结果

2射频变压器参数如下:

输入单端阻抗:50 Ohm

阻抗变换比:1:1

频率范围:0.4MHz~500MHz

带内插损 (Spec.):≤ 3dB

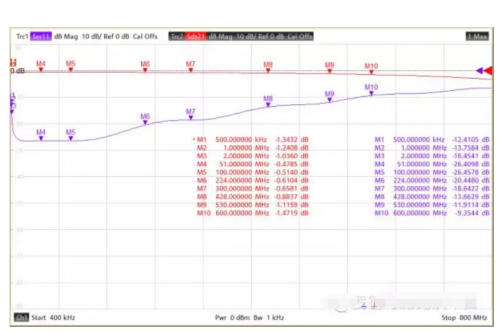

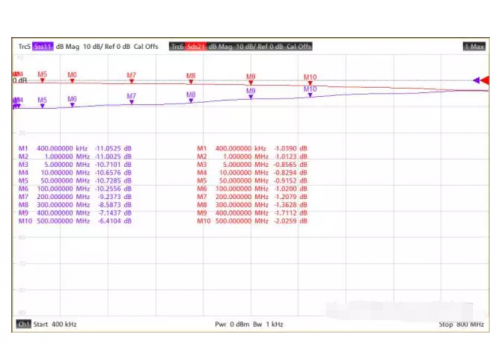

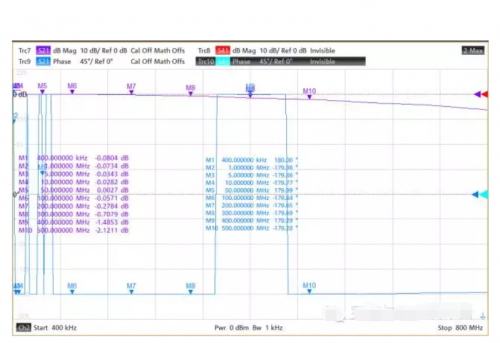

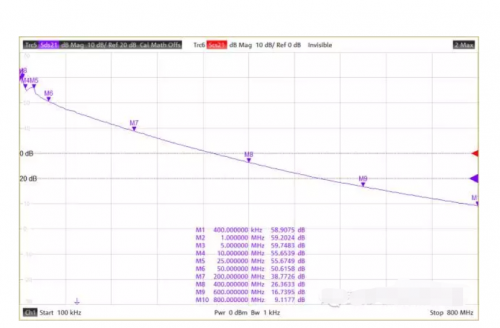

按照上面所描述的测试步骤,经校准、端口延伸,并将差模和共模阻抗分别设置为50 Ohm、12.5 Ohm后,测试结果如图8、9所示,插损满足规格指标,幅度和相位不平衡特性也相对较好。图10给出了共模抑制比CMRR的测试结果,这是使用矢网的Trace Math功能得到的结果,现在矢网已经支持直接显示CMRR测试结果,使得测试更加方便。

图9#变压器幅度和相位不平衡特性测试结果

图10#变压器CMRR测试结果

通过以上两个测试实例表明,对于这种单端阻抗非50 Ohm的射频变压器测试,与传统的back-to-back测试法及阻抗变换器测试法相比,使用矢网络分的虚拟差分测试模式及端口延伸等功能将更加方便,可以在不改变测试装置的情况下,直接测试变压器的插入损耗、回波损耗、幅度和相位不平衡特性以及共模抑制比CMRR等,极大程度简化了射频变压器的测试。

射频变压器的测试虽然可以当做balun,射频变压器仍然比较特殊,因为具有阻抗变换比,比如1:1、1:2、1:4等,而且单端阻抗不一定为常用的50 Ohm系统阻抗。那么射频变压器的差分阻抗和共模阻抗是多少呢?

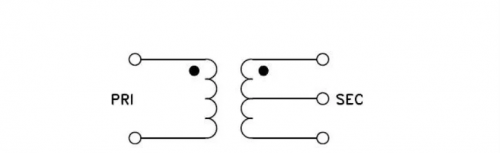

图11给出了射频变压器的典型示意图,初级线圈PRI端为单端,次级线圈SEC端为平衡端。假设输入阻抗(单端阻抗)为50 Ohm,阻抗变换比为1:2,则差分阻抗为输入阻抗与阻抗比之积,为100 Ohm,共模阻抗差分阻抗的四分之一,即25 Ohm。

图11. 典型的射频变压器示意图

这是射频应用中经常用到的balun,单端50 Ohm/差分100 Ohm。射频变压器的阻抗比多种多样,单端阻抗也不一定是50 Ohm,表1给出了几个不同阻抗变换比和输入阻抗的例子,以便于理解。

表1. 多种阻抗比和输入阻抗对应的差模和共模阻抗

之所以关注这些参数,是因为在矢网端口参考阻抗设置中需要分别设定。

介绍完差分阻抗和共模阻抗的计算方法之后,下面再聊一聊矢网的端口延伸技术——Offset。Offset功能是有一定前提的,即认为被补偿的网络(比如PCB走线)是理想的:(1) 非色散;(2) 在校准参考面处理想匹配;(3) 互易。

Offset功能根据反射测试计算出待补偿网络的传输特性,从而使得测试参考面延伸至DUT的pin. 因其应用基于一些理想的情况,所以是有局限性的,精度也是有限的。

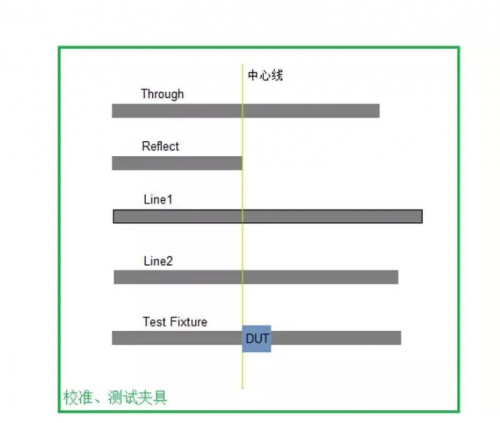

除了使用Offset功能外,还有一种精度更高的校准方法——自制TRL校准件,可以直接将测试参考面校准至DUT的pin处。图12给出了自制TRL校准件的示意图,包含Through、Reflect(一般设计为开路)、Line校准件及测试夹具。之所以将TRL校准件与测试夹具制作在一起,是因为这样可以最大程度规避加工误差及介质基板均匀性等因素给测试带来的影响。

图12. 自制TRL校准件示意图

关于TRL校准,后面有时间会专门介绍,此处仅作简要说明。TRL校准方式非常适用于SMT表贴这种非同轴连接的DUT测试,这类器件的测试需要借助于测试夹具或者评估测试板,而TRL可以直接将测试参考面校准至pin处,那么如何做到这一点呢?

能否校准至pin处,与TRL校准件的尺寸设计及矢网中设置的校准件参数有关。比如,将Through的长度设计为为测试夹具中DUT两侧PCB走线的长度之和,此处假设这两段走线长度相同;将反射校准件Reflect的长度设计为Through长度的一半。

在矢网中将Through的电长度设置为0,就相当于选择pin处为校准参考面。Reflect的参数可以不用设置,TRL校准不需要已知其参数,只要保证校准时,矢网的两个端口是连接的同一个Reflect校准件即可。一般将Reflect设计为开路。

TRL校准件存在适用的校准频率范围,这取决于Line与Through电长度的差异。该校准方式要求Line与Through的电长度之差不能为中心频率半波长的整数倍,否则校准数据中会存在坏值。从相位的角度讲,在中心频率处,一般建议二者的相差在20°~160°之间。由此可以推算出适用的频率范围为:

f_start=1/18 ? c/l , f_stop=4/9 ? c/l

式中,c为信号在基板中的相速度,l 为Line与Through的电长度之差。

为了扩展适用的频率范围,还可以使用多条Line,例如图10中使用两条Line。甚至再引入Match校准件,从而完成向更低频率的扩展。